2025年4月8日

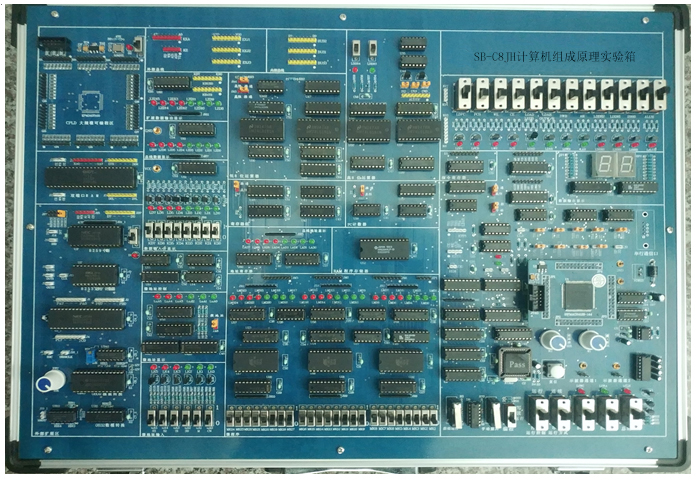

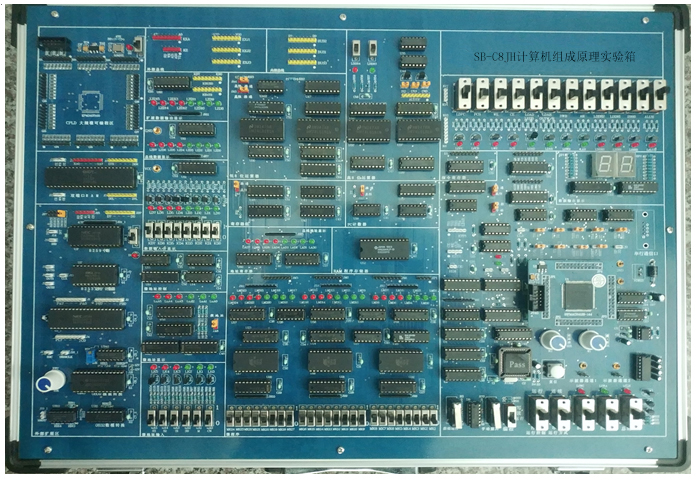

SB-C8JH计算机组成原理实验箱

一、结构特点

计算机组成原理实验箱由铝木合金箱体、高性能稳压电源、系统控制部件、开放式实验电路区等组成。全部实验用信号线的连接采用排线,操作方便,接触可靠。基础实验基于中小规模集成电路,综合性实验基于在系统可编程核心器件,资源完全向学开放,可以完成"计算机组成原理"、"计算机结构与逻辑设计"、"在系统编程"、"VHDL设计"、"电子系统综合设计"等课程的实验,并可以进行"专用集成电路设计"的验证实验。本实验箱适用于本专科院校计算机专业和其它相关专业的相关课程的实验和创新设计。

二、技术性能

1、硬件系统采用高性能单片机89S52和LATTICE公司CPLD器件的有机结合,使系统的硬件控制电路精简而可靠。

2、提供手动、自动和联机三种工作方式,满足不同层次实验的监视需要。

3、具有完善的系统检测电路和系统保护电路设计,使实验系统更易于维护和使用。

4、系统自备双通道逻辑示波器,便于实验过程中时序信号的测量。

5、系统和电脑采用RS232/USB通信方式。

6、实验系统采用总线结构,使实验计算机具有结构简单清晰、扩展方便、灵活易变等诸多优点,实验时只要少些接线即可。

7、扩展FPGA实验模块,实现复杂模型机的设计实验。

8、专为本机配备的动态集成调试运行软件以图形化的界面显示模型机内部数据的流向和各种控制信号的状态以及时序关系。

三、硬件技术指标

1、实验电路工作电源:+5V/2A、±12V/0.5A,每路均带有短路保护和自动关断功能,每路带电源指示。其中+5V电源设计有过压、过流、欠压保护功能,待电路中故障排除后,自动恢复供电,确保设备和人身安全。

2、实验系统的字长为8位、16位兼容设计。

3、实验系统的基本指令系统类PC

机,有多种指令格式,多种寻址方式。

4、主存储器采用8K字节静态存储器6264,用于存放用户程序和数据。

5、配运算器模块,由4片4位的算术逻辑单元功能发生器级联而成。每片内实现16种二进制算术运算及16种逻辑运算,可进行8位、16位运算器实验。

6、控制器采用微程序方案实现,控存字长为24位,可用最大容量为1024字节,且用电可擦写的E2ROM存储器芯片组成,支持动态微程序设计。

7、实验系统工作频率源由555时基电路和74LS123可再触发单稳态多谐振荡器组成产生,频率范围为330HZ~580HZ。可以同时产生四种不同时序的时钟信号。

8、实验系统配有微程序手动输入并显示模块,装有24个微程序输入开关,用于输入微程序。

9、配有手动16位数据输入模块,装有16个数据输入开关,用于输入16位数据。

10、配8个控制开关,2个微动开关,用于手动控制整机的运行和切换运行方式等。

11、配2位七段数码管以显示程序运行的结果。另配置6个数码管,用于交通灯显示。

12、配微地址发生器模块和微地址显示模块、微地址控制模块。

13、配数据总线显示模块,用于显示数据总线上的动态数据。

14、配总线地址显示模块,用于显示地址总线上的动态地址。

15、配有一个双向通用移位寄存器,以实现逻辑移位功能。

16、具有超前进位控制逻辑。

17、配有指令寄存器和地址寄存器。

18、主机上设计有大规模

CPLD 和超强51单片机作为整机的主控器件,可以在完全自动方式下完成全部部件实验和整机模型机设计实验。

19、配有并行I/O接口电路8255,实现带输入输出接口的模型机的设计。

20、配有定时/计数器接口电路8253。实现带定时/计数器功能的模型机的设计。

21、配有中断控制器8259。实现带中断功能的模型机的设计。

22、配有双端口存储器IDT7132。

23、模数A/D和数模D/A转换电路,实现数模和模数的转换。

24、扩展ALTERA

EPM240核心模块,实现具备多功能复杂模型机的设计实验。

25、实验的连接:模块间实验线路的连接:全部信号采用排线连接,操作简便,实验导线连接稳定可靠。

26、外形尺寸:480×360×148mm。

27、机箱:铝木合金材料,绿色环保。

四、软件技术指标

1、实验系统集成动态调试运行软件。

2、详尽的CAI课件,能将实验原理、实验目的、芯片、查询等功能集于一体,便于多媒体教学;

3、极强的程序和微程序调试功能,有单步、断点和连续等运行方式。

4、有程序和微程序读写功能。

5、以彩色流程图方式全程监视程序的运行状态和运行结果。

6、读写存贮菜单,对寄存器进行输入数据和参数设置以及读出目标输出信息。

五、实验项目

1、8位算术逻辑运算实验

2、带进位控制8位/16位算术逻辑运算实验

3、超前进位算术逻辑运算实验

4、移位运算器实验

5、存储器实验

6、微控制器实验

7、基本模型机的设计与实现

8、带移位运算的模型机的设计与实现

9、

复杂模型机的设计与实现

10、扩展8255并行口实验

11、扩展8253定时/计数器实验

12、扩展8259中断控制器实验

13、扩展AD转换实验

14、扩展DA转换实验

15、扩展双端口存储器实验

16、可重构原理计算机组成设计实验

17、基于CISC和RISC处理器构成的实验计算机的设计与实现

18、总线控制实验

19、硬布线控制器实验

20、乘法器设计实验

21、FIFO先进先出存储器实验

22、数据通路实验

23、基于流水技术构成模型计算机的实验

|

电工电子技能综合实训考核平台 |

|

电工电子技术综合实训考核装置 |

|

电工基础与技能实训考核装置 |

|

电工技术综合实验平台 |

|

电工技术综合实训装置 |

|

电工综合实训考核平台 |

|

电工技术实训网板 |

|

电子工艺实训台(两面4工位) |

|

电子技术综合实训考核设备 |

|

电子技术综合实验装置 |

|

模拟与数字电路实验平台 |

|

模数电实训平台 |

|

数模电综合实训平台 |

|

电气自动化设备安装与维修实训考核平台 |

|

维修电工技能实训考核装置(网孔板、双组型) |

|

网孔型电工技能及工艺实训考核装置(双面、四组) |

|

智能型装接表电工实训系统 |

|

电工技能实训考核柜 |

|

直流调速(调压)实训控制柜 |

|

电气工程与自动化实训室设备 |

|

化工自动化仪表实训平台 |

|

电工·电子技术实训装置 |

|

电气控制实训装置(单面双组型) |

|

电工电气控制实训考核装置 |

|

电气装配综合实训装置 |

|

电气装调实训装置 |

|

电气装配与调试实训平台 |

|

仪表自动化控制综合实训台 |

|

中级电工实训考核设备 |

|

高级电工实训考核设备 |

|

初中高级维修电工实训考核装置 |

|

高性能高级维修电工及技能培训考核实训装置 |

|

维修电工电气控制及仪表照明电路实训考核装置 |

|

电工电子电拖综合实验装置 |

|

现化电工综合实训考核实训台 |

|

减速机与电机实训装置 |

|

电工培训考核装置 |

|

电机拖动及运动控制综合实验台 |

|

机电技术技能实训考核装置 |

|

电机控制与调速实训装置 |

|

电机与电气控制实训台 |

|

楼宇智能化控制系统平台 |

|

电气技能实训考核装置 |

|

电工电气装配与工艺实训台 |

|

电机与电力拖动实训装置 |

|

维修电工技能实训考核装置(网孔板、单面双组型) |

|

电工电子及电机拖动综合实训平台 |

|

电工电子电力拖动技术实验装置 |

|

电工技能实训与考核装置 |

|

电工技术实训台 |

|

电工技术实验装置 |

|

电工电子电力拖动实验与技能实训台 |

|

电工综合实训考核设备 |

|

高级电工实训台 |

|

电工电子综合实验台 |

|

智能型电工电子拖动综合实验装置(带PLC实验) |

|

电工基本技能训练实训装置 |

|

电子技术综合应用创新实训考核装置 |

|

电子技术创新设计综合应用实训装置 |

|

电子焊接实训考核装置 |

|

电子工艺与检测实训平台 |

|

电子产品装配实训台 |

|

电子装配实训台 |

|

电子技术实验装置 |

|

高级电工电子技术实验装置 |

|

高性能电工电子电拖综合实训装置 |

|

电子技术综合实验装置 |

|

电子电路综合实验实训装置 |

|

电子电工基础实验台、通用电工实验装置 |

|

通用电力拖动实训装置 |

|

电工基础实验装置 |

|

电气控制技术实训考核装置 |

|

电气控制及电子技能实训考核装置 |

|

内外线电气安装与维修实训装置 |

|

网孔型电工技能及工艺实训考核装置(单面、双组) |

|

电工技能实训考核平台 |

|

电工电子技能及创新设计综合实训考核装置 |

|

电工电子与电力拖动实训平台 |

|

电工电子技术实验台 |

|

初、中、高级及技师维修电工实训考核装置 |

|

电工技能训练工作台 |

|

电工技能实训教学装置 |

|

电气控制综合实验装置 |

|

供配电技术实训装备 |

|

维修电工技能训练与考核平台(网孔板、双组型) |

|

电工实训装置(单面双组型) |

|

电工电子模拟实训装置 |

|

低压电工电气装配实训台 |

|

电子装调工作台 |

|

电子装配工艺与检测实训装置 |

|

电工工艺(维修电工)试验台 |

|

电工电子电拖实训台 |

|

一体化电工电子技术创新设计综合应用实训装置 |

|

现代维修电工技术实训考核装置 |

|

电工电子实训台 |

|

电工电子实训设备 |

|

电工实训工作台 |

|

电子技术技能实训考核台 |

|

电子学技术综合实验装置 |

|

维修电工电气控制实训装置 |

|

机床电气与PLC控制教学实验装置 |

|

维修电工技能考核实训装置 |

|

机电技术技能实训考核装置 |

|

电气装配实训装置(网孔板、双组型) |

|

学生电源台,学生电源实训装置 |

|

电子产品设计与制作实训平台 |

|

电子单片机实训台 |

|

维修电工实训设备 |

|

维修电工实训考核装置 |

|

电机电力电子及电气传动实训装置 |

|

电机控制及调速综合实训装置 |

|

电工电子自动化综合实训实验台 |

|

模电数电综合实验装置 |

|

电工模电数电综合实训平台 |

|

电气控制及电子技能实训考核装置 |

|

电气装配实训装置 |

|

网孔型电工电气装配实训台 |

|

维修电工实训考核装置(单面双工位) |

|

电子电工综合实验装置 |

|

电工电子综合实训平台 |

|

电源控制实训平台 |

|

电工技能测试台 |

|

电工操作台、初级维修电工实训设备 |

|

电子综合实验平台 |

|

电工综合实验平台 |

|

维修电工实训设备 |

|

高级电工技能实训考核装置 |

|

电工电子技术创新设计综合应用实训台 |

|

电力拖动实验装置 |

|

电工电子技术实验台 |

|

高级电工技术实验台 |

|

电工综合实验装置 |

|

维修电工技能智能实训考核装置 |

|

机电技术技能实训考核装置 |

|

电工电子技能综合实训装置 |

|

通用电工竞赛训练平台 |

|

高级电工练功考核实训台 |

|

电工、电子、电力拖动、PLC、变频器、单片机、触摸屏实训台 |

|

电子技术综合实训装置 |

|

电子技术技能实训台 |

|

现代物流仓储自动化实验系统 |

|

电气线路安装实训装置 |

|

维修电工技术实训平台 |

|

电力电子技术应用实训装置 |

|

电工电子综合应用创新实训装置 |

|

电气照明设备安装调试技能实训装置 |

|

电气安装调试实训设备,电气安装调试实训装置 |

|

自动生产线装调与设计实训装置 |

|

互联网+现代电工电子技术实训装置 |

|

电工电子·电拖·PLC技术综合实训考核装置 |

|

电气设备安装调试技能实训装置 |

|

电工电子基础实验装置 |

|

电工电子技术基础实训考核平台 |

|

电气安装与维修实训装置 |

|

电机传动与控制实验装置 |

|

维修电工高级技师考核实训设备 |

|

电气技术考核实训装置 |

|

电气控制PLC实训台 |

|

电气安装与维修实训考核装置 |

|

电气控制系统安装与调试实训设备 |

|

电机及电气技术实验装置 |

|

电气安装调试实训装置 |

|

通用电工电子电拖实验装置 |

|

电工电子实验装置 |

|

电力拖动及运动控制综合实验装置 |

|

电机拖动及电气控制技术实训装置 |

|

电机拖动及运动控制综合实验台 |

|

机电综实训考核平台 |

|

电力拖动实验装置 |

|

电工电子技术创新设计综合应用实训台 |

|

计算机组装与维修实训装置 |

|

电力电子技术应用创新设计综合实训装置 |

|

全数字交流调速系统实验装置 |

|

直流调速技术实训装置 |

|

电机性能测试柜 |

|

机电控制综合实训平台 |

|

电机控制实训台 |

|

电机控制接线实验台 |

|

电机运动控制实训装置 |

|

电工电机拖动实训装置 |

|

电机装配与运行检测实训装置 |

|

电机电控配线安装实训装置 |

|

电机·变压器维修及检测实训装置 |

|

电机故障检测实训考核装置 |

|

变频器工作原理实训装置 |

|

维修电工技能实训考核装置(电气控制·PLC·变频器) |

|

维修电工电气控制技能实训装置 |

|

网孔型高级电工综合实训考核装置 |

|

高级电工技能实训考核装置 |

|

高级维修电工变频调速PLC可编程控制实训装置 |

|

高级维修电工实训平台 |

|

电子产品工艺实训台 |

|

电子焊接技能实训平台 |

|

现代电工技术实训考核装置(柜式、双面型) |

|

高级电工电子实验装置 |

|

数字电子技术综合实训考核装置 |

|

模拟电路、数字电路实验平台 |

|

电子学综合实验装置 |

|

模拟电子电路实验装置 |

|

模拟电路应用创新实验平台 |

|

电子装配及焊接技能实训装置 |

|

电子焊接实训考核装置 |

|

电子焊接装配实训台 |

|

电子产品焊接与工艺实训台 |

|

电子工艺焊接装配生产线 |

|

电工电子创新综合实训装置 |

|

电子工艺实训考核装置 |

|

电子工艺实训考核装置 |

|

电子创新实验台 |

|

电子产品设计与装调实训考核装置 |

|

电力拖动一体化实训设备 |

|

网孔型电工电子电力拖动PLC可编程综合实训装置 |

|

网络型高性能电工电子技术实训与考核装置 |

|

智能电子电路综合实训台 |

|

模电数电综合应用创新实训考核装置 |

|

电子(模电数电)技术综合应用创新实训考核装置 |

|

智能化电工职业技能等级考核平台 |

|

电工高级技能鉴定实训考核设备 |

|

电工电子基础实验实训教学平台 |

|

电工电子综合实验装置 |

|

电子技术综合实训考核平台 |

|

电工实训考核装置 |

|

电工技能实训装置 |

|

电工技能实训台 |

|

电工技能实训教学装置 |

|

电气系统安装与调试实训装置 |

|

电工技术实训室、电工技术实训室设备 |

|

电工基础实训台 |

|

电工实训考核装置,电工技术实训考核装置,网孔型电工实训考核设备 |

|

现代电气控制系统安装与调试实训考核装置 |

|

网孔型电气控制实训装置 |

|

在线智慧电子实验系统综合实训平台 |

|

电子产品装调与人工智能创新考核装置 |

|

电力电子技术应用创新设计综合实训装置 |

|

电子学综合实验装置 |

|

双面四工位低压电工技能实训考核装置 |

|

电工实训操作台(单面二组型) |

|

电工电子技术综合实训考核装置 |

|

电工电子自动化综合实验实训装置 |

|

电工电子电拖实验装置 |

|

电工技能鉴定实训装置 |

|

低压电气装配工技能实训考核装置 |

|

电工电拖综合实训装置 |

|

电工技术实训考核装置 |

|

机电综合实训考核平台 |

|

电工电子技术实验装置 |

|

电力拖动实训装置 |

|

电工PLC实训考核装置 |

|

轨道交通电力系统综合自动化技能实训考核平台 |

|

电机与拖动综合实训平台 |

|

电力电子及电机拖动实验装置 |

|

电力电子综合实训平台 |

|

电力拖动一体化实训设备 |

|

电力系统综合自动化技能实训考核平台 |

|

电力系统微机保护综合实训装置 |

|

电力系统自动化实训平台 |

|

电气设备及二次部分实训考核装置 |

|

电机电力电子及电气传动教学实验台 |

|

现代电力电子及交直流调速实验装置 |

|

电力电子技术实验箱 |

|

电力电子技术实训装置 |

|

电机及电气技术实验装置 |

|

电机电力电子及电气控制技术实验装置 |

|

电机及电气技术实验装置 |

|

交直流调速实训装置 |

|

大功率直流调速系统实训考核装置 |

|

电机装配与运行检测实训考核设备 |

|

电机电力拖动及电气控制实训装置 |

|

电机拖动及自动控制系统实验台 |

|

电机及电气控制实验装置 |

|

电子技术综合实训装置 |

|

电子焊接装配实训台 |

|

电子创新综合实训平台 |

|

电工电拖综合实训平台 |

|

电机控制实验台、电机PLC控制实验装置 |

|

摇臂钻集合实验台,机床电气控制技能实训考核装置 |

|

电气控制实训平台 |

|

一体化网络型高级维修及技师电工技能培训考核实训装置 |

|

防爆电气控制技术技能培训考核实训装置 |

|

电机及拖动实验台 |

|

电气综合控制实训考核装置 |

|

高级电工电子实训装置 |

|

高级维修电工综合实训柜 |

|

电工操作实操台,网孔型电工技能实训考核装置 |

|

电气安装实训装置 |

|

电工电子综合应用创新实训装置 |

|

电动机装配实训装置 |

|

电机维修及检测实验装置 |

|

机电传动与控制实训装置 |

|

电机控制与调速实训装置 |

|

电力拖动电气控制实验装置 |

|

电工电气实训考核装置 |

|

电工电子实训台 |

|

电机拖动与调速系统实训装置 |

|

电子产品设计及制作生产线 |

|

电力系统微机保护综合实训设备 |

|

电子技术综合实验装置 |

|

电子技术综合实训平台 |

|

网孔型高级维修电工实训设备,网孔型中级维修电工实训设备,网孔型初级维修电工实训设备 |

|

高级电工电拖实训考核柜、中级电工电拖实训考核考核柜、初级电工电拖实训考核考核柜 |

|

机电传动与PLC控制实验台 |

|

电力拖动PLC变频调速综合实训装置 |

|

电力拖动实训台 |

|

电工基础及基本技能实训台 |

|

电机拖动实训设备 |

|

电子技术实验实训室设备 |

|

电工电子实训考核装置 |

|

高级电工电子电力拖动实验装置 |

|

供电技术实训装置 |

|

电力拖动与控制技术实训装置 |

|

电力电子及电气传动实验台 |

|

电力技术控制系统实训演示设备 |

|

电工电子及电力拖动综合应用创新实训装置 |

|

高性能电工电子电力拖动综合实验装置 |

|

电力自动化仪表及过程控制实训平台 |

|

电力系统继电保护实验台 |

|

电气控制实训室设备 |

|

电气控制技术实验装置 |

|

维修电工实训考核装置 |

|

高级电工及技师维修电工实训考核装置 |

|

维修电工实训装置、维修电工技能操作台 |

|

高级维修电工考核实训台(单面双组型) |

|

电气安装与维修实训考核装置 |

|

电工电力电子实训平台 |

|

电力拖动及电机控制实训台 |

|

电机及拖动控制实训平台 |

|

大功率直流调速系统实训考核装置 |

|

转速、电压、电流负反馈直流调速系统的安装和调试实训系统 |

|

电力系统综合自动化实验平台 |

|

供配电所实训装置 |

|

变电二次安装工实训考核装置 |

|

工厂供电综合自动化实训装置 |

|

供配电实验室设备,电气工程综合实训设备 |

|

电工基本操作技术实训室设备 |

|

机电驱动实训设备 |

|

电子产品装配实训室 |

|

电气控制技能实训考核装置 |

|

电气安装与维修实训考核设备 |

|

电子焊接防静电实训台 |

|

电子产品装配与调试生产线 |

|

电子工艺实训考核装置 |

|

模拟电路实验装置 |

|

电机技术实验装置(交/直流发电机) |

|

电机与变压器综合实验装置 |

|

电力拖动.PLC技能实训装置,电力拖动、PLC实训装置 |

|

高性能高级维修电工及技能培训考核实训装置 |

|

高级电工职业技能鉴定综合实训考核装置 |

|

电力自动化及继电保护实验装置 |

|

电力自动化及继电保护实验台 |

|

电力拖动(工厂电气控制)实验装置 |

|

初中级电工实训考核装置 |

|

高级电工技术实验台 |

|

电气智能控制PLC 技术实训装置 |

|

电力电子与电力传动专业课程 |

|

电力电子技术实验室设备 |

|

电气安装与维修实训考核装置 |

|

自动化综合实训装置 |

|

高级维修电工实训考核装置 |

|

电工实训考核装置简介,电气装配实训台注意事项 |

|

高性能高级维修电工技能培训考核装置 |

|

电子技术实训装置 |

|

电工电子技术创新设计综合应用实训装置 |

|

电气动力设备安装调试技能实训装置(高级) |

|

(初级)电气动力设备安装调试技能实训装置 |

|

(中级)电气动力设备安装调试技能实训装置 |

|

电气照明设备安装调试技能实训装置 |

|

高性能电工技术实验台 |

|

高低压配电实验实训装置 |

|

电工技术综合实验装置 |

|

数字电路应用创新实验平台 |

|

一体化教学电工技术工作岛 |

|

电工技术实验装置 |

|

模拟电路实验装置 |

|

电工技能实训考核装置 |

|

高性能电工电子电力拖动综合实训装置 |

|

高性能电工综合实验装置 |

|

高级电工实操柜,中级电工实操柜,初级电工实操柜 |

|

高级电工技术实训考核装置 |

|

中级电工技术实训考核装置 |

|

初级电工技术实训考核装置 |

|

通用电工技能综合实训装置 |

|

电工PLC实训考核装置 |

|

电工综合训练装置 |

|

电工实训装置 |

|

电工实验装置 |

|

电工电子综合实验装置 |

|

电工电子电拖实训装置 |

|

电工·电子技术实训装置 |

|

现代高级电工电拖实训考核设备 |

|

中高级电工可编程触摸屏变频器数模电实训台 |

|

维修电工电气控制实训考核装置 |

|

仪表及照明单三相电机控制实训考核装置 |

|

高级电工综合实验装置 |

|

现代电气控制应用实训设备 |

|

通用电工实验台,通用电工技术实训台 |

|

通用电子实验台 |

|

通用电工电子实验台 |

|

通用电工电子电力拖动实验台 |

|

通用电工电子电力拖动带直流电机实验台 |

|

电工、电子、电力拖动(带直流电机、三相可调)实验装置 |

|

通用电力拖动实验室成套设备 |

|

通用电力拖动实验室成套设备(带直流电机实验) |

|

通用电工电子 电力拖动

直流电机实验室设备 (四合一) |

|

现代电气控制系统安装与调试实训装置 |

|

电工·电子·电拖创新实训室设备 |

|

工匠人才创新工作室实训设备 |

|

电气实训操作台 |

|

可编程变频器电气控制综合实训装置 |

|

现代电气控制综合实训装置 |

|

电工技术实验装置 |

|

电工电子技术实训装置 |

|

智能型电工电子技术实验装置 |

|

智能型电工、电子、电力拖动综合实验装置 |

|

智能型电工、电子、电力拖动综合实验装置(带PLC实验) |

|

智能型电工、电子/电拖、PLC、单片机综合实验装置 |

|

智能型电工、电子、电拖、PLC、变频调速综合实验装置 |

|

电子技术创新设计综合应用实训装置 |

|

电子焊接装配生产线 |

|

电子焊接工作台 |

|

电子工艺实训台 |

|

电子装配调试实训台 |

|

电子产品装调一体化创新实训装置 |

|

电子电工技术实训室设备 |

|

电气装配实训台(单面双组型) |

|

机床PLC电气控制实训考核装置 |

|

电气装配实训台 |

|

电工技能训练与考核平台(网孔板、双组型) |

|

电气技能实训考核装置(单面双组型) |

|

高性能电工技术实验装置 |

|

高性能电工电拖实验装置 |

|

高性能电工、电子、电力拖动、PLC、变频器实训装置 |

|

高级电工技术实验台 |

|

高性能电工电子实验台 |

|

高级电工电子电拖综合实验台 |

|

维修电工技能实训考核装置(两面四组型) |

|

维修电工技能实训考核装置(网孔板、双组型) |

|

初级电工、电拖实训考核装置(柜式) |

|

中级电工、电拖实训考核装置(柜式) |

|

高级电工、电拖实训考核装置(柜式) |

|

高性能高级维修维修电工实训考核装置 |

维修电工电气控制及仪表照明电路综合实训考核装置 |

高级维修电工实验考核系统 |

高级维修电工技能实训考核装置 |

仪表照明实训考核装置 |

高级维修电工实训考核装置 |

|

维修电工电气控制及仪表照明电路综合实训考核装置 |

|

高级技师维修电工实训考核装置 |

|

网络维修电工高级技师实训智能考核装置 |

|

维修电工电气控制技能实训考核装置 |

|

技能大师工作室设备、技能创新实验实训设备 |

|

高级电工实训考核鉴定装置 |

|

智能型现代电气控制实训考核装置 |

|

高性能初级维修电工及技能培训考核实训装置 |

|

高性能中级维修电工及技能培训考核实训装置 |

|

高性能高级维修电工及技能培训考核实训装置 |

|

电工电子综合应用创新实训装置 |

|

高级电工、电拖、PLC实训考核装置 |

|

西门子S7-1200高性能高级维修电工实训考核平台 |

|

电工电气控制实训考核装置 |

|

电气照明接线实操考核平台 |

|

电气设备安装调试技能实训装置 |

|

自动加工与装配生产线实训考核设备 |

|

网孔型万能电气控制与及机床电路实训考核鉴定装置 |

|

机床电气技能实训考核鉴定装置 |

|

现代电气控制系统安装与调试实训考核装置 |

|

模电、数电、电力拖动实验台 |

|

维修电工实训考核柜(柜式、双面型) |

|

低压电工考核实训装置 |

|

低压电气控制实训台 |

|

电工技能实训试验台 |

|

电气与维修综合实训考核平台 |

|

网孔型电工技能实训台 |

|

网孔型维修电工实训装置 |

|

双面网孔板维修电工技能实训考核装置 |

|

高级电工电子实验装置 |

|

电工电拖实训平台 |

|

维修电工电气控制技能实训考核装置 |

|

维修电工通用型实训考核实训装置 |

|

维修电工排故培训考核装置 |

|

电工基本技能综合实训设备 |

|

维修电工实训装置(网孔板单面双组型) |

|

电工电子技术·电力拖动实训考核装置 |

|

通用电工电子电拖(带直流电机)实验台 |

|

电子基础技能实训考核平台 |

|

电子技术实验教学平台 |

|

电子技术综合实训考核装置 |

|

电工电子技术实训考核装置 |

|

电工实训装置 |

|

电工电子实验装置 |

|

电工电子电力拖动实验装置 |

|

电工电子电力拖动实验装置(带PLC实验) |

|

电子产品装调与智能检测实训考核装置 |

|

电子基本技能实训考核设备 |

|

电子产品装调与人工智能创新考核装置 |

|

电子基本技能实训考核设备 |

|

电子工艺实训考核装置 |

|

电子工艺综合实训装置 |

|

电子工艺实验考核装置 |

|

电工技能及工艺实训考核装置(网孔板) |

|

通用电工电子技术及电力拖动实验台 |

|

电子产品焊接装配实训台 |

|

智能电工实训考核装置 |

|

多功能维修电工教学实训考核装置 |

|

中级维修电工实训台 |

|

初级维修电工实训学生台 |

|

电子实验室设备 |

|

电工电子综合实验平台 |

|

模电数电技术实验台 |

|

电机电力电子与交直流调速实验台、电机电力电子与电气传动技术实验装置

|

|

智能供配电实训装置 |

|

智能变配电系统实验开发平台 |

|

高级维修电工及技师技能实训考核装置 |

|

交流变极调速系统(至少3速)电气实训柜 |

|

工厂供配电实训装置 |

|

供配电技术综合实验装置 |

|

高低压配电实验实训装置 |

|

低压供配电技术实训设备 |

|

低压配电成套实训装置 |

|

低压配电操作实训室设备 |

|

工厂供电综合自动化实训系统 |

|

工厂供电技术实训装置 |

|

35kV变电站及10kV供配电系统倒闸操作屏 |

|

变配电室值班电工技能培训考核系统 |

|

供配电所实训装置 |

|

智能供配电实训装置 |

|

工厂供电及配电自动化实验装置 |

|

变电站综合自动化实训系统 |

|

微机及继电保护实验实训装置 |

|

电力系统继电保护综合实验装置 |

|

电力系统继电保护与自动化实训装置 |

|

电力系统微机线路保护实训考核装置 |

|

电力系统继电保护工培训考核平台 |

|

电力系统自动化实训平台 |

|

电力系统继电保护与自动化实训装置 |

|

电力系统继电特性及继电保护实验装置 |

|

电机及自动控制实验装置 |

|

高级维修电工实训设备 |

|

电气PLC控制实训平台 |

|

中级维修电工实训考核装置 |

|

维修电工中级技能实训设备 |

|

高性能初级维修电工技能实训装置 |

|

电气安装与维修实训考核装置 |

|

电气动力设备安装调试技能实训装置 |

|

电工电气维修实训台 |

|

维修电工与PLC实训考核装置(双工位) |

|

电气系统安装与调试实训装置 |

|

维修电工技能实训考核台 |

|

高级技师维修电工实训装置 |

|

维修电工技师、高级技师技能实训考核装置 |

|

维修电工仪表照明实训考核装置 |

|

维修电工电气控制及仪表照明电路综合实训考核装置 |

|

维修电工电气控制技能实训考核装置 |

|

智能低压电工实训考核鉴定设备 |

|

电工实训操作实操台 |

|

安全用电实训考核装置 |

|

电子实训装配生产流水线 |

|

新能源发电实训设备 |

|

电工、模电、数电、微机接口及微机应用实验设备(适用于高校、大专、职业学院)

更多产品>> |

|

电力电子技术及数模电综合实验台 |

|

电工、模电、数电实验室设备 |

|

模拟 数字电子电路微机接口

微机应用综合实验室设备 |

|

信号与系统·控制理论·计算机控制技术实验台 |

|

模电、数电、通信原理教学实验装置综合实验台 |

|

电工模电数电电气控制(直流电机)实验装置 |

|

模电、数电、现代通讯原理实验室成套设备 |

|

高级模电、数电综合实验台 |

|

模电、数电、高频电路综合实验台 |

|

模电、数电、自动控制综合实验台 |

|

模电、数电、单片机实验开发系统综合实验台 |

|

电工基础实验室设备、电工实验装置 |

|

电工实验室成套设备 |

|

电工基础实训装置 |

|

电工实验台 |

|

电工、模电、数电、电气控制综合实验室成套设备 |

|

模电.数电实验台 |

|

电工、模电、数电实验台(三合一) |

|

电工、模电、数电、电气控制实验台(四合一) |

|

电工、模电、数电、电气控制(带直流电机)实验台(五合一) |

|

电机拖动及电力电子技术创新实验实训装置 |

|

电力电子与电力牵引实验台 |

|

电力电子技术实验装置 |

|

电力电子技术及电气传动实训装置 |

|

电力电子电气自动控制技术实训装置 |

|

电力电子及交直流调速实验装置 |

|

电机及电气技术实验装置 |

|

电力电子实训装置 |

|

电力电子技术实验台 |

|

电力电子基础实训台 |

|

电力电子技术实训台 |

|

电力电子技术实训装置 |

|

电力电子及电机拖动综合实验装置 |

|

电力电子技术及电机控制实验装置 |

|

电力电子及电气传动实训装置 |

|

电力电子技术实验装置 |

|

电机控制及照明实训柜 |

|

电力自动化及继电保护实验装置 |

|

DSP原理及电机调速实验系统 |

|

现代电工技术实训考核装置 |

|

现代电力电子技术实验设备 |

|

电工电子电气技术实训装置 |

|

电机拖动及电气控制技术实验装置 |

|

电机维修及检测实训装置,控制微电机综合实验装置,电机拖动实训设备 |

|

电机原理及电机拖动实验系统 |

|

单双闭环直流调速控制实训装置 |

|

交直流调速实训装置 |

|

电机维修及检测实训设备 |

|

机电综实训PLC考核平台 |

|

电机拖动实验台 |

|

电机及电气技术实验装置 |

|

电气动力设备安装调试技能实训装置 |

|

电力电子与电机拖动技术实验台 |

|

电力电子电机拖动综合实验台 |

|

电机控制与调速综合实训装置 |

|

电力电子技术及电机控制实验装置 |

|

电工电子综合应用创新实训装置装置 |

|

通用电力拖动实验装置 |

|

电力拖动实训装置 |

|

电工电子相关实验教学设备 |

|

电子装配实训台,电子基本技能实训设备 |

|

电机及电气技术实验装置 |

|

电力电子技术实训装置 |

|

电子技术综合实训考核装置 |

|

电子、单片机技术综合实训考核装置 |

|

电子技术及传感器综合实训装置 |

|

电子技术综合实训平台 |

|

电子应用技能实训考核装置 |

|

电工技术实训装置 |

|

电工电子技术实验台 |

|

电工、模电、数电、电力拖动(带直流电机)实验与实训考核台、电工维修实训设备 更多产品>> |

|

模拟混合综合实验平台 |

|

数电模电实验平台 |

|

模电、数电实验与技能实训考核台 |

|

电工、模电、数电实验与技能实训考核台 |

|

通用电工、电子、电拖实验与电工、电子、电拖技能实训考核实验室设备 |

|

电工、模电、数电、电力拖动(带直流电机)实验与技能实训考核实验室设备 |

|

电工、模拟、数字、电力拖动综合实验装置 |

|

电工技能实训与考核实验室成套设备 |

|

电工·模电·数电·电拖·单片机·PLC·传感器技术综合实训考核装置 |

|

电工、模电、数电、电气控制、PLC可编程控制综合实验装置 |

|

电工、电子、电拖(带直流电机)实验与电工、电子、电拖技能实训考核实验室设备 |

|

电气装配与工艺实训台 |

|

网孔型电工电子技能及工艺实训考核装置 |

|

网孔型电力拖动(工厂电气控制)技能及工艺实训考核装置 |

|

维修电工仪表照明实训考核装置 |

|

初级工实训台、中高工实训台、高级工实训台 |

|

高性能电工电子电拖综合实训装置 |

|

高性能电工电子技术实训考核装置 |

|

高性能电工、电子、电力拖动技术实训考核装置 |

|

电力拖动工厂电气控制技能及工艺实训考核装置、网孔型电工电子电力拖动变频调速PLC装置 |

|

高性能电工电子电拖及自动化技术实训与考核装置 |

|

高性能电工技术实训考核装置、高性能电工电子技术实训考核装置、高性能电工电子电力拖动技术实训考核装置 |

|

电子技术综合实训考核装置,电工电子技术实训考核装置,电工电子技术·电力拖动实训考核装置 |

|

电力拖动·PLC技能实训装置、电力拖动技能实训考核装置 |